Always Can Be Used in Describing Combinational Logic

Read Free Combinational Logic Design With Verilog Combinational Logic Design With Verilog Simple Combinational Logic Design in VerilogECE 2372002 October 28th Combinational Log. Programming constructs like for loops can be used to make this description more concise but they do not imply any sequential or procedural behavior.

Always can be used preceding a case statement.

. ITo create hierarchy and create combinatorial logic gates we use the always comb block. As we discussed in the post on verilog operators there are two main classes of digital circuit which we can model in verilog combinational and sequential. When we use this construct we effectively tell our compiler and synthesis tools to enforce stricter rules.

Its usually recommended to use a Casez rather than a Casex statement. To use blocking and non-blocking assignment in always construct to describe a combinatioanl logic the following 2 methods do work but which is the. Always can be used in describing memory made of flip-flops and registers.

Clock buffers also known as global buffers BUFG are primitives that can take a regular signal as an input and connect to a clock net on the output side. In a previous article we discussed the use of the Verilog assign keyword to perform a continuous assignment. Instead the Design Compiler expands or unrolls loop constructs to form a combinational logic function.

Begin statements end. A few design examples were shown using an assign statement in a previous article. 14 alwaysposedgeClock Blocks alwaysposedgeClock always at the positive edge of the clock or alwaysnegedgeClock al-ways at the negative edge of the clock blocks are used to describe Sequential Logic or Registers.

RTL assumes that all clock edges occur in the same event region and data changes in the next region. If the the combinational logic is used the the generation or gating of clocks or other aysynchrounous resetssets then non-blocking assignments could generate races or glitches. In this post we discuss one of the most important constructs in verilog - the always block.

However we still have to be careful about the errors. It also shows how to utilize the Verilog always block for describing combinational circuitsan always block can provide us with an even easier solution to describe a digital circuit. Always sensitivity-list invalid Verilog code.

We saw that the Verilog Casex and Casez statements can simplify the code when there are dont-care values in our truth table. Here you can add Result to get the feed back update. The buffers have a high fan-out to minimize skew while driving the numerous other primitives that utilize the clock signal.

Always can be used in describing Combinational logic. Combinational Logic II Prof. In addition all of the inputs to the multiplexer were specified in the sensitivity list.

True this is because always is a procedural block or sensitivity list and any statements within the block are executed sequentially. IThese statements inherited from procedural languages provide a powerful means of expression. If you use an intra-assignment delay like A 10 B.

To model a multiplexer an if statement was used to describe the functionality. That statement evaluates RHS variable B the blocks the combinational always process for 10 time units then assigns the value to the LHS variable A and proceeds to the next statement. Combinational Logic with always - ChipVerify Verilog Combinational Logic.

Only. IInside the always comb block we describe the behavior of combinational logic in a sequential algorithmic way with if else while and case statements. A previous article showed different examples of using an always block to implement combinational logic.

Where the sensitivity list is manually defined. Always can be used in describing Combinational logic. In Verilog one module can instantiate other modules and can have multiple instances of another module.

A JK flip flop is one of the many types of flops used to store values and has two data inputs j and k along with one for. The purpose of these rules is to help ensure that we have correctly modelled our logic circuit. Always can be used in describing memory made of flip-flops and registers.

An alternative solution which I highly discourage is to replace the always_comb with The IEEE1364-1995 style of combinational logic. Always ALU_control or adder_rlt or add_rlt or or_rtl or xor_rtl or Result. Systemverilog always_comb Block.

A few design examples were shown using an assign statement in a previous article. The code snippet above outlines a way to describe combinational logic using always blocks. But the key point about a blocking assignment is the LHS variable gets its value before proceeding to the next statement.

In contrast to combinational logic sequential circuits use a clock and require storage elements such as flip. Always can be used in describing Combinational logic. The same set of designs will be explored next using an always block.

In Verilog one module can instantiate other modules and can have multiple instances of another module. We can use the always_comb block when we want to model a combinational logic circuit in SystemVerilog. Always can be used preceding a case statement.

For a Combinational logic this means that a piece of code could be ran once it reaches the always statement. The same set of designs will be explored next using an always block. The one exception to this rule is when an ouput is not specified for all possible values of the inputs.

Combinational Logic with always The verilog always block can be used for both sequential and combinational logic. Such assignments are always active and can be used to acquire a. Assignments are used when specifying combinational logic see Section15.

This article examined the use of the Verilog If and Case statements for describing a combinational circuit. An always block is also mainly used to implement sequential logic which has memory elements like flip flops that can hold values. If the clocks start moving into into different regions you get race conditions.

Usagi Combinational logic The output is a pure function of its current inputs The output doesnt change regardless how many times the logic is triggered Idempotent Sequential logic The output depends on current inputs previous inputs their history 2 Recap. Combinational Logic with always The verilog always block can be used for both sequential and combinational logic.

Combinational Logic With Always

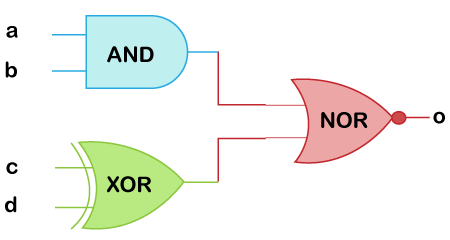

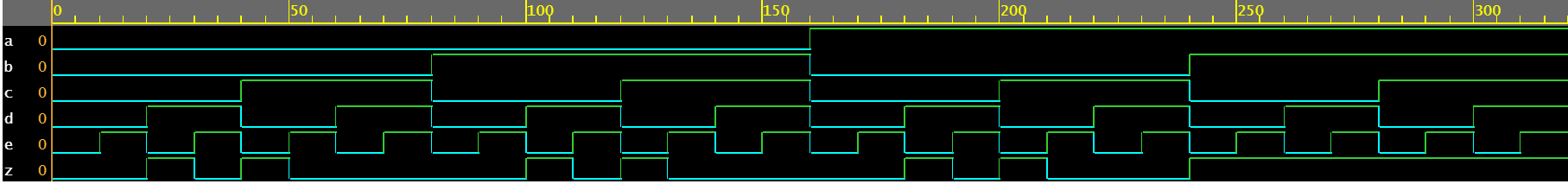

Describing Combinational Circuits In Verilog Technical Articles

Describing Combinational Circuits In Verilog Technical Articles

Conic Section Kids Encyclopedia Children S Homework Help Kids Online Dictionary Conic Section Kids Homework Parabola

Another Neat Option For My 1st Graders Classroom Discipline Plan Classroom Behavior Classroom Discipline

The 12 Houses Of The Zodiac Meanings A Grouped Images Picture Zodiac Meanings Zodiac Signs Astrology Zodiac

How I Teach Phonics Giveaway Freebie Teaching Phonics Phonics Teaching

Verilog Always Block Javatpoint

Pin By ประภ สสร เร องพย งศ กด On Education For Learning English Adjectives English Grammar Learn English

Combinational Logic With Always

Describing Combinational Circuits In Verilog Technical Articles

Arduino Brushless Motor Control Tutorial Esc Bldc Howtomechatronics Arduino Circuit Diagram Circuit

Combinational Logic With Always

Combinational Logic With Always

.png)

Describing Combinational Circuits In Verilog Technical Articles

Combinational Logic With Always

Combinational Logic With Always

Combinational Logic With Always

Plr Private Label Rights For Your Online Courses And Ebooks Private Label Ebooks Online Labels

Comments

Post a Comment